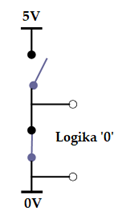

Rangkaian digital merupakan rangkaian yang tersusun dari komponen digital dan menggunakan notasi sinyal digital. Sinyal digital yang pada umumnya diketahui hanya memiliki dua nilai saja yaitu sinyal logika rendah (‘0’) dan sinyal logika tinggi (‘1’). Untuk sistem tegangan DC 5V, logika rendah (‘0’) direpresentasikan dengan tegangan 0V, sedangkan logika tinggi (‘1’) direpresentasikan dengan tegangan 5V (ligat gambar 1).

Gambar 1. Representasi logika ‘0’ dan ‘1’ dalam rangkaian

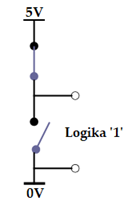

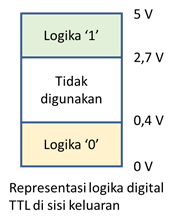

Karena adanya derau dan ketidakidealan dalam rangkaian digital, terdapat toleransi dalam representasi logika ‘0’ dan ‘1’. Pada standar transistor-transistor logic (TTL) logika ‘0’ berada di rentang 0 – 0.8 volt untuk sisi masukan dan rentang 0 – 0,4 volt untuk sisi keluaran. Sedangkan logika ‘1’ berada di rentang 2 – 5 volt untuk sisi masukan dan rentang 2,7 – 5 volt untuk sisi keluaran sebagaimana ditunjukkan pada gambar 2.

Gambar 2. Rentang nilai untuk logika ‘0’ dan ‘1’ pada standar transistor transistor logic (TTL)

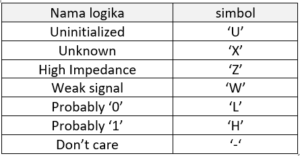

Tahukah anda jika selain logika ‘0’ dan logika ‘1’, ternyata masih ada kemungkinan logika lainnya yang dikenal dalam sistem digital. Logika tersebut diberikan dalam tabel 1 berikut ini.

Tabel 1. Logika digital selain ‘0’ dan ‘1’

Bagaimana realitas logika digital tersebut dalam rangkaian? Marilah kita bahas satu per satu.

- Kondisi ‘U’ atau uninitialized merupakan suatu keadaan yang muncul di awal saat nilai logika belum dipastikan berlogika ‘1’ atau ‘0’. Jadi, Nilai ’U’ hanya muncul di awal saja sebelum logika lainnya. Tidak ada nilai ‘U’ yang tiba-tiba muncul di tengah setelah sebelumnya bernilai logika ‘1’ atau ‘0’.

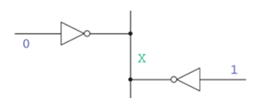

- Nilai ‘X’ atau unknown merupakan kondisi digital yang mencul ketika logika ‘1’ bercampur dengan logika ‘0’ dalam suatu titik. Sebagai ilustrasi perhatikan gambar 3 berikut ini. Dua buah gerbang inverter masing-masing outputnya bertemu di suatu titik. Gerbang inverter pertama memiliki input logika ‘0’ sehingga logika outputnya berlogika ‘1’, sedangkan gerbang inverter kedua memiliki input logika ‘1’ sehingga outputnya berlogika ‘0’. Namun karena output kedua gerbang inverter bertemu pada suatu titik, maka logika yang muncul bukan logika ‘0’ atau ‘1’ namun kondisi unknown atau ‘X’.

Gambar 3. Kondisi yang menyebabkan munculnya logika ‘X’

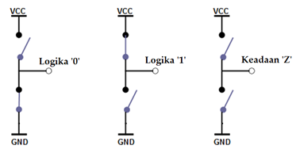

- Kondisi high impedance atau ‘Z’ merupakan kondisi dalam rangkaian digital yang tidak tersambung ke logika ‘1’ atau ke logika ‘0’. Gambar 4 menunjukkan ilustrasi munculnya ‘Z’ di output karena terputus dari tegangan VCC (sebagai logika ‘1’) dan terputus dari tegangan 0 (sebagai logika ‘0’). Berbeda dengan ‘U’ yang hanya muncul di awal, nilai ‘Z’ dapat muncul dimanapun asalkan titik tersebut memang tidak tersambung ke ‘1’ maupun ‘0’.

Gambar 4. Kondisi high impedance ‘Z’

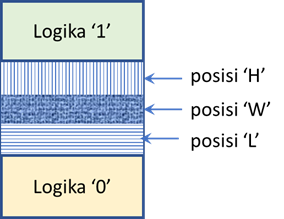

- Keadaan weak signal atau ‘W’ merupakan keadaan dimana tegangan di suatu titik bernilai tengah-tengah antara tegangan logika ‘1’ dan ‘0’. Kondisi Probably ‘0’ atau ‘L’ berada di bawah ‘W’ sampai dengan sebelum masuk logika ‘0’, dan kondisi Probably ‘1’ atau ‘H’ berada di atas ‘W’ sampai dengan sebelum masuk logika ‘1’. Posisi ‘W’, ‘L’, dan ‘H’ diilustrasikan dalam gambar 5 di bawah ini. Nilai ‘H’, ‘W’ dan ‘L’ dapat terjadi karena beberapa faktor, diantaranya

- karena jalur perambatan data antara satu gerbang ke gerbang lainnya berjauhan sehingga terjadi drop tegangan yang cukup besar

- kesalahan rangkaian yang menyebabkan tegangan yang dihasilkan tidak bisa mendekati nilai logika ‘1’ maupun ‘0’.

- Beban fan out yang terlalu besar sehingga arus yang disuplai oleh suatu gerbang tidak mencukupi dan berakibat tegangan yang dihasilkan menjadi lebih kecil.

Gambar 5. Ilustrasi posisi ‘H’, ‘W’ dan ‘L’ diantara logika ‘0’ dan ‘1’

Info Penulis

Dr. Eng. Hendra Setiawan, S.T., M.T.

Electronics, FPGA, Signal Processing, Wireless communication physical layer

Email : [email protected]